- 您现在的位置:买卖IC网 > Sheet目录1999 > ICS9E4101AFILFT (IDT, Integrated Device Technology Inc)IC TIMING CTRL HUB PROG 56SSOP

IDTTM

Programmable Timing Control HubTM for Intel Systems

1408A—01/25/10

ICS9E4101

Programmable Timing Control HubTM for Intel Systems

17

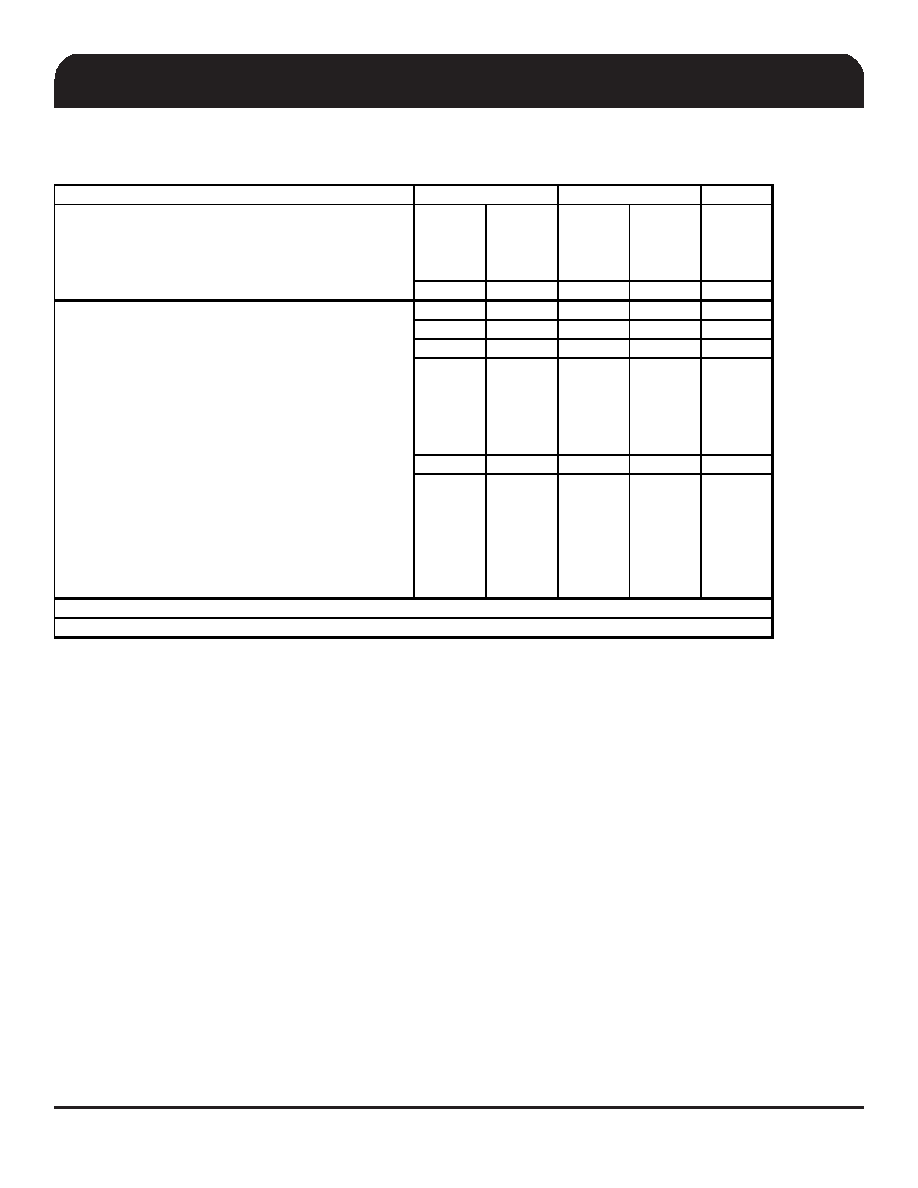

Test Clarification Table

Comments

FS_C/TEST

_SEL

HW PIN

FS_B/TEST

_MODE

HW PIN

TEST

ENTRY

BIT

B6b6

REF/N or

HI-Z

B6b7

OUTPUT

0X

0

X

NORMAL

10

X

0

HI-Z

10

X

1

REF/N

11

X

0

REF/N

11

X

1

REF/N

0X

1

0

HI-Z

0X

1

REF/N

B6b6: 1= ENTER TEST MODE, Default = 0 (NORMAL OPERATION)

B6b7: 1= REF/N, Default = 0 (HI-Z)

HW

SW

FS_C/TEST_SEL is a 3-level latched input.

o Power-up w/ V >= 2.0V to select TEST

o Power-up w/ V < 2.0V to have pin function as

FS_C.

When pin is FS_C, VIH_FS and VIL_FS levels

apply.

FS_B/TEST_MODE is a low-threshold input

o VIH_FS and VIL_FS levels apply.

o TEST_MODE is a real time input

TEST_SEL can be invoked after power up through

SMBus B6b6.

o If TEST is selected by B6b6, only B6b7 controls

TEST_MODE. The FS_B/TEST_Mode pin is not

used.

Power must be cycled to exit TEST.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS9EX21801AKLF

IC FANOUT BUFF DIFF 72-VFQFN

ICS9EX21831AKLF

IC FANOUT/BUFFER DIFF 72VFQFN

ICS9FG1901HKLFT

IC FREQUENCY GENERATOR 72-QFN

ID82C54

IC OSC PROG TIMER 8MHZ 24DIP

IDT2308A-4DCI8

IC CLOCK MULT ZD HI DRV 16-SOIC

IDT2309-1HPGGI

IC CLK BUFFER ZD HI DRV 16-TSSOP

IDT2309A-1HPGG

IC CLK BUFFER ZD HI DRV 16-TSSOP

IDT2309B-1HPGGI

IC CLK BUFFER HIGH DRIVE 16TSSOP

相关代理商/技术参数

ICS9EMS9633BKILF

功能描述:IC EMBEDDED PC MAIN CLK 48VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS9EMS9633BKILFT

功能描述:IC EMBEDDED PC MAIN CLK 48VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS9EMS9633BKLF

功能描述:IC EMBEDDED PC MAIN CLK 48VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6

ICS9EMS9633BKLFT

功能描述:IC EMBEDDED PC MAIN CLK 48VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS9EPRS475BGLF

制造商:Integrated Device Technology Inc 功能描述:IC EMBEDDED PC MAIN CLK 56TSSOP

ICS9EPRS475BGLFT

制造商:Integrated Device Technology Inc 功能描述:IC EMBEDDED PC MAIN CLK 56TSSOP

ICS9EPRS475CGLF

功能描述:IC EMBEDDED PC MAIN CLK 56TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS9EPRS475CGLFT

功能描述:IC EMBEDDED PC MAIN CLK 56TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT